728x90

1. 컴퓨터의 특성

- 호환성 : 서로 다른 컴퓨터 간에도 프로그램이나 자료의 공유가 가능

- 신뢰성 : 주어진 환경에서 아무 고장 없이 담당 기능 및 문제 처리를 원할하게 수행할 수 있는 척도

- 범용성 : 일부분에 국한되지 않고 다목적으로 사용

- 자동성 : 작성된 프로그램에 의해 자동으로 처리

- 정확성 : 컴퓨터에서 처리된 결과는 정확함

- 신속성 : 컴퓨터의 처리 속도는 빠름

- 대용량성 : 대량의 자료 처리 및 보관이 가능

2. 중앙처리장치

연산장치와 제어장치가 있으며 넓은 의미로 주기억장치가 포함되기도 한다.

제어 장치에서 연산 장치와 주기억 장치로 제어 신호를 내보내고, 연산 장치에서 데이터의 연산이 이루어진 다음 그 결과를 주기억 장치로 보내는 기능을 함

- 중앙처리장치(CPU) : 제어장치, 주기억 장치, 연산 장치

- 주변 장치 : 입력 장치, 출력 장치, 보조 기억 장치

3. 레지스터

※ 레지스터 : 데이터를 담고 있는 영역

- 명령어 레지스터 (IR) : 현재 실행 중인 명령어를 기억하는 레지스터

- 프로그램 카운터 (PC) : 다움에 수행할 명령어의 번지(주소)를 보관

- MAR (Memory Adress Register) : 기억번지레지스터, 기억장치의 주소를 기억

- MBR (Memory Buffer Register) : 기억버퍼레지스터, 기억장치를 통해 접근되는 정보의 내용 기억

- 누산기 (ACCumulator) : 산술 및 논리 연산의 결과를 일시적으로 기억

- 인덱스 레지스터 ( Index Register ) : 인덱스 주소 지정 시 사용되는 레지스터

- 메모리 레지스터 ( Memory Register ) : 한 비트를 저장할 수 있는 플립플롭의 모임. CPU 내 임시 기억 장치

4. 불 대수

| 합의 법칙 | 곱의 법칙 |

| A + 0 = A | A • 0 = 0 |

| A + 1 = 1 | A • 1 = A |

| A + A = A | A • A = A |

| A + Ā = 1 | A • Ā = 0 |

5. 기본 논리 회로 - XOR

배타적 논리합(XOR), 둘 중 하나의 값이 1일 때만(서로 다를 때) 출력값이 1이 됨.

6. 기본 논리 회로 - NOT

NOT 게이트(인버터, Inverter)는 입력값의 반대값이 출력됨.

2진수 1의 보수를 구하는데 사용

7. 기본 논리 회로 - AND, OR

- AND : 두 개의 입력 스위치가 직렬로 연결, 둘 다 동시에 ON 상태에서 불이 켜지므로 A=1, B=1이 됨

- OR : 두 개의 입력 스위치가 병렬로 연결, 둘 중 하나만 ON이면 불이 켜짐

8. 반가산기(HA: Half Adder)

- 2진수 1자리(1Bit)의 A와 B를 더한 합(Sum)과 자리올림수(Carry)를 얻는 회로

- 입력 : 2개(A,B), 출력: 2개(S, C)

- AND회로와 XOR 회로로 구성

- 진리표에 의해 출력된 합(Sum)은 배타적 논리합(XOR) Gate의 진리표이고, 자리올림수(Carry)는 논리곱(AND)의 진리값과 같음

9. 플립플롭 ( Flip-Flop )

- 플립플롭 (Flip-Flop) : 1비트( '0' 또는 '1')의 정보를 기억할 수 있는 최소의 기억 소자

- 플립플롭의 종류 : RS 플립플롭, JK 플립플롭, D 플립플롭, T 플립플롭 등

10. JK 플립플롭

- JK 플립플롭 : J = K = 1이 되면 반전

- JK 플립플롭은 RS플립플롭에서 S=R=1인 경우 발생하는 문제점(부정)을 보완개선한 플립플롭으로 모든 플립플롭의 기능을 대용할 수 있다.

- J = 0, K = 0 -> 전 상태 불변, J = 0, K = 1 -> 0, J=1,K=0 -> 1

11. RS 플립플롭

- RS 플립플롭에서 S=1, R=1이면 출력은 부정(불능) 상태가 됨

- RS 플립플롭에서 S=0, R=0이면 출력은 전 상태 불변이 됨

- RS(Reset/Set) Flip-Flop

12. 그레이코드

- 비가중치 코드 중 한 숫자에서 다음 숫자로 증가할 때 한 비트만 변함

- '2진수 -> 그레이코드' , '그레이코드 -> 2진수' 두 가지 변환 방법이 있음

13. 연산

- AND 연산 : 둘 다 1인 경우 1이 됨

- 결과가 동시에 1인 경우 1이 되므로 AND 연산이 적용된 경우임

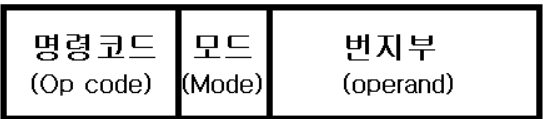

14. 명령어

명령어의 형식은 명령 코드부(OP-Code)와 번지부(Operand)로 구성됨

※인스트럭션(Instruction) : 일을 시키는 단위

15. 주소형식

0-주소 형식 ( =스택구조 )

- 명령어에 오퍼랜드부가 없어 데이터가 명령어 자체에 있는 방식(연산자만 존재)

- 스택 구조의 컴퓨터에서 사용(번지가 묵시적으로 지정)

- 연산 속도가 가장 빠름

1-주소형식 ( =ACC(누산기)구조 ) : 주소(오퍼랜드부)가 하나 존재

2-주소형식 ( = 범용레지스터 구조) : 주소부가 2개인 가장 일반적 형식

3-주소형식 ( = 범용레지스터 구조) : 명령어에 오퍼랜드부가 3개 존재하므로 원래 값이 보존됨

16. 주소지정방식

- 직접 주소 지정(Direct Addressing) : 주소 부분에 있는 값이 실제 데이터가 있는 주기억 장치 내의 주소를 나타냄, 메모리 참조 1회

- 간접 주소 지정(Indirect Addressing) : 명령어의 주소 부분으로 지정한 기억 장소의 내용이 실제 데이터가 있는 곳의 주소로 사용됨. 메모리 참조 2회 이상

17. 입출력 채널

- 멀티플렉서 채널(Multiplexer Channel) : 저속의 여러 입출력 장치(프린터, 카드) 를 여러 개의 서브 채널이 있어 동시에 조작할 수 있는 채널 ( = Byte Multiplexer Channel)

- 셀렉터채널 (Selector Channel) : 주기억 장치와 고속의 입출력 장치(자기테이프, 자기디스크) 간에 데이터를 전송하는 프로세서로 한번에 한개의 장치를 선택하여 동작

- 블록 멀티플렉서 채널(Block Multiplexer Channel) : 블록 단위로 이동시키는 채널, 멀티플렉서채널과 셀렉터 채널의 복합 형태

18. 레지스터

버퍼 레지스터(Buffer Register) : 읽거나 기록한 데이터를 일시적으로 기억하는 레지스터로 입출력 장치나 전자 계산기 내부의 동작 속도를 맞추기 위해 사용됨

728x90

'knowledge > IT-license' 카테고리의 다른 글

| [ 정보처리기능사 필기] 4. 정보 통신 일반 (0) | 2023.01.15 |

|---|---|

| [ 정보처리기능사 필기 ] 3. PC 운영체제 (1) | 2023.01.14 |

| [ 정보처리기능사 필기] 2. 패키지 활용 (1) | 2023.01.13 |

![[ 정보처리기능사 필기 ] 1. 전자계산기 일반](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdn%2FcdrdUL%2FbtrVVQ21ICH%2FuXsYXwSZYxxM3IhK9yfhtK%2Fimg.png)